“我(wǒ)(wǒ)OpenBox又(yòu)回來了!”

沉寂了16個月,終于又(yòu)提筆開(kāi)始寫《硬件二層交換設計與實現》。從軟件設計到硬件設計需要這麽長時間嗎(ma)?答案是肯定的,不僅需要,而且這點時間還隻能初入Verilog代碼編程之門。

但從網絡實驗教學的角度來看,這是不可接受的。故我(wǒ)(wǒ)們想換個思路,走走捷徑。然而這一(yī)走,便走了整整16月有餘。

所幸略有小(xiǎo)成,與君分(fēn)享,共勉自學、自研、自證之艱辛與快樂。

A)P4與Tofino

書(shū)上或網上能找到的内容請大(dà)家自行查找了解。見:https://p4.org

B)FAST全軟件可編程平台

FAST架構在我(wǒ)(wǒ)們之前的文章中(zhōng)有介紹,該平台也是一(yī)種典型的SDN架構設計,硬件數據平面主要包括FPGA OS和UM兩部分(fēn),核心邏輯處理在UM模塊中(zhōng)。UM又(yòu)分(fēn)成了5個不同邏輯功能流水線,

用戶可以針對此流水線進行改造升級或擴展新的流水級功能。然而,使用Verilog語言來開(kāi)發FPGA芯片功能着實是一(yī)件比較有難度的事情,至少在成爲一(yī)個合格的Verilog代碼工(gōng)程師之前來說,确實有比較漫長和艱辛的路程要走。

受P4編程思想的啓發,我(wǒ)(wǒ)們決定将FAST架構中(zhōng)的UM部分(fēn)更換成具備P4開(kāi)發能力的硬件邏輯部件。故該平台依然采用多核CPU加FPGA架構,P4邏輯全采用FPGA編寫,所有功能和指令邏輯全在硬件實現。

C)基本功能

1.分(fēn)組前96字節内,小(xiǎo)于128的任意bit位,任意多個PHV對象定義;

2.支持32字節Metadata對象編程,含16字節用戶自定義Metadata内容;

3.分(fēn)組前60字節内,任意bit位對象查表匹配,精确匹配與帶掩碼匹配,匹配字段支持輸入端口等Metadata字段;

4.每動作支持14條指令,支持加、減、與、或、異或、取反等操作;

5.每個指令執行器中(zhōng)含16個臨時寄存器,支持臨時變量暫存與讀取,位寬支持1到64位;

6.支持有狀态的存儲寄存器對象定義與操作,存儲寄存器位寬支持1到64位,最大(dà)個數支持128個。支持多個寄存器對象編程;

7.支持對分(fēn)組進行協議插入與删除,長度支持1到16字節;

8.動作與指令均支持參數化配置,即可運行前實例化,也可運行時調整;

9.支持32種不同邏輯業務處理功能在線編譯、在線加載、在線配置、在線卸載,不影響其他業務邏輯;

10.提供P4後端編譯器,支持用戶P4代碼編譯;

11.提供P4運行時配置管理工(gōng)具,支持用戶流表配置、動作配置和寄存器初始配置。

擁有上述平台編程功能後,對硬件的設計要求便會變得較爲簡單。原來要花較長時間,寫較多代碼的功能,現在可以簡單、快速的實現。

A)設計原理

從交換機的幾個功能步驟開(kāi)始,先實現源MAC地址的學習。從平台功能分(fēn)析,使用寄存器部件比較合适。

拟定義一(yī)個端口與MAC地址的映射表,存儲在寄存器對象中(zhōng),使用源MAC地址作爲寄存器對象的索引,分(fēn)組輸入端口号作爲該索引位置的值。在使用目的MAC查表時,亦使用MAC地址作爲索引進行查找,即可獲取該地址學習存儲的端口号。

由于MAC地址爲48位,本平台支持寄存器的深度有限,故本案例中(zhōng)僅取MAC地址的後4位作爲索引。故實驗演示時,要求測試主機的MAC地址尾數不同。

單播地址可以采用上述思路進行設備,那組播與廣播地址呢,我(wǒ)(wǒ)們本案例拟采用全泛洪的方式先來實現一(yī)個基礎版本。

想要做組播功能可以将組播協議配置規則送CPU處理,CPU學習到入組和退組信息後,通過P4的運行時工(gōng)具進行組播MAC與相應端口号的規則配置即可。

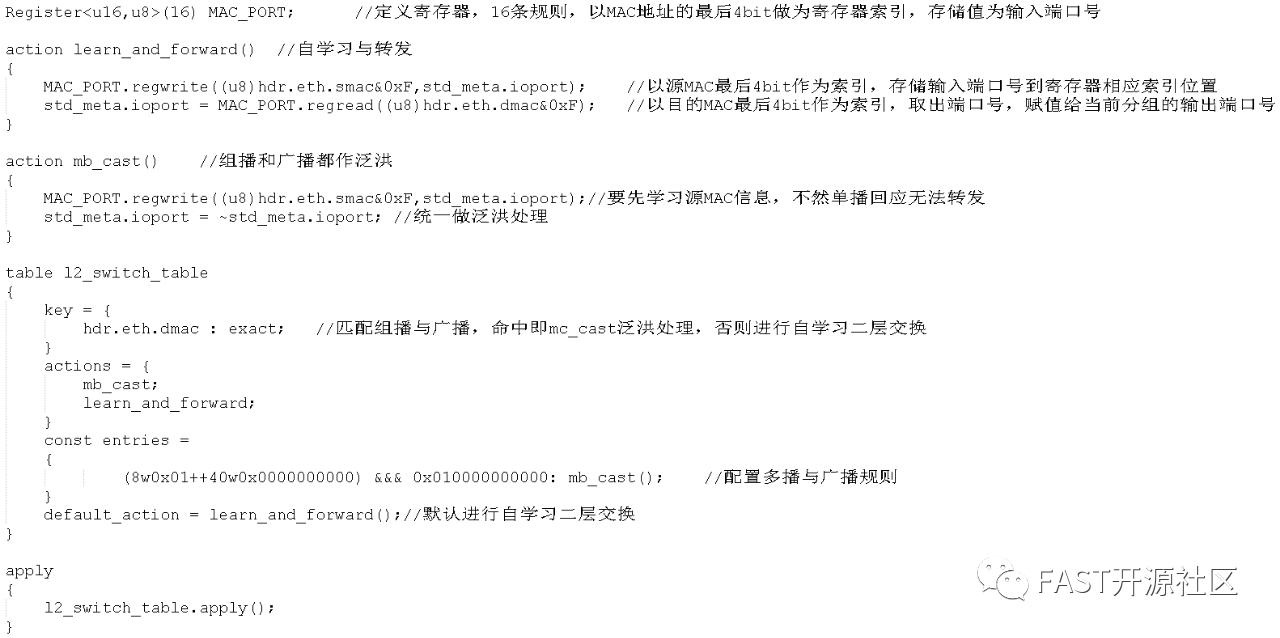

B)代碼實現

action learn_forward()

{

MAC_PORT.regwrite((u8)hdr.eth.smac&0xF,std_meta.ioport);

std_meta.ioport = MAC_PORT.regread((u8)hdr.eth.dmac&0xF);

}

單播自學習與轉發

action mb_cast()

{

MAC_PORT.regwrite((u8)hdr.eth.smac&0xF,std_meta.ioport);

std_meta.ioport = ~std_meta.ioport;

}

多播泛洪

以上爲硬件二層交換機(原型系統)全部業務邏輯功能代碼。是的,就是這四行代碼!!!!

A)軟件核心代碼

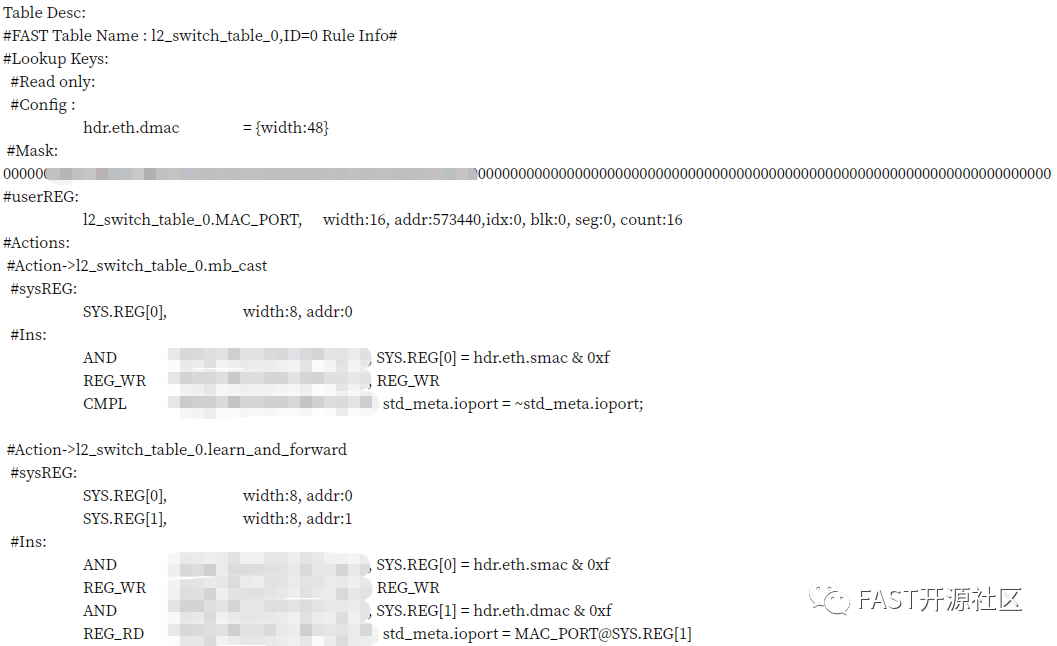

B)編譯器結果

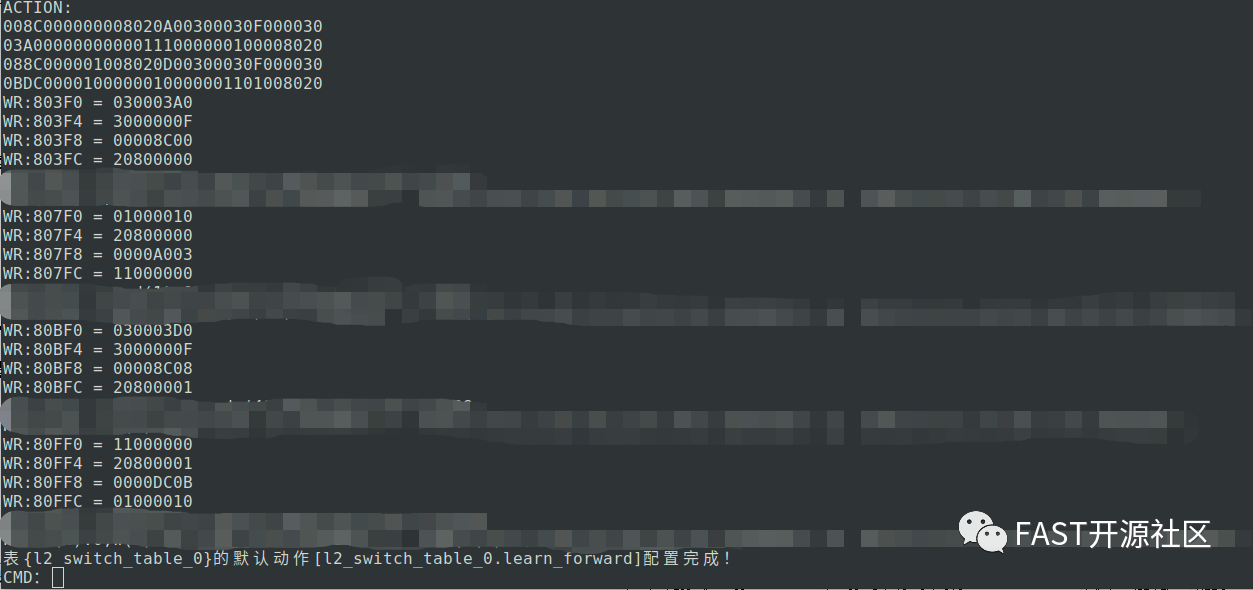

C)硬件配置

D)Ping通測試

C:\Users\Administrator>ping 192.168.1.198

正在 Ping 192.168.1.198 具有 32 字節的數據:

來自 192.168.1.198 的回複: 字節=32 時間<1ms TTL=127

來自 192.168.1.198 的回複: 字節=32 時間<1ms TTL=127

來自 192.168.1.198 的回複: 字節=32 時間<1ms TTL=127

來自 192.168.1.198 的回複: 字節=32 時間<1ms TTL=127

物(wù)質守恒、能力守恒,苦難亦然守恒。

爲了讓學生(shēng)們在我(wǒ)(wǒ)們平台編寫硬件邏輯少些痛苦,我(wǒ)(wǒ)們艱苦奮鬥了16個月,對P4的原理、代碼和編譯器進行了仔細琢磨、分(fēn)析和領悟。我(wǒ)(wǒ)們認爲P4是一(yī)門較爲優秀的編程語言,更是一(yī)種硬件編程的創新思路和具體(tǐ)表達形式。我(wǒ)(wǒ)們無法去(qù)破解P4的硬件實現,固然也無從參考,而是領悟P4編程方式的精髓理念後,采用了原有FAST架構和部分(fēn)邏輯調整,并配置P4後端編譯适配,打造了現如今的支持P4的FAST架構可編程平台。

本平台結合了FAST架構與P4可編程的雙重優勢。支持用戶在最底層硬件到最高層軟件全方便的編程與驗證,而且編程語言均使用C語言和類似C的P4語言,進一(yī)步降低了學習與使用難度。

下(xià)一(yī)步,做個硬件路由器?或者您有更美好的想法,我(wǒ)(wǒ)們可以試一(yī)試!

有需要開(kāi)發可編程硬件(FPGA、ASIC等)的P4後端編譯器,或獲得本平台介紹相關源碼的客戶,請與15116127200(微信同号)聯系,閱讀更多FAST相關文章請進入以下(xià)公衆号。